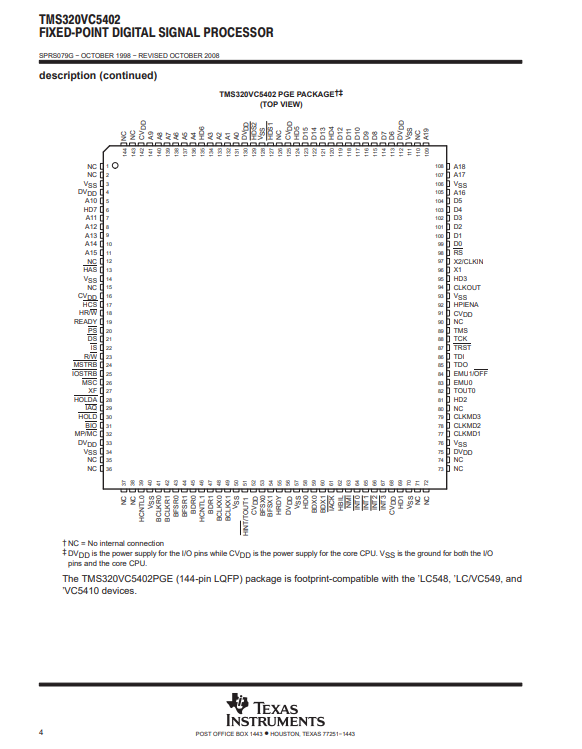

TMS320VC5402PGE100 IC DIG SIG PROCESSORE 144-LQFP

Parametro del prodotto

Descrizione

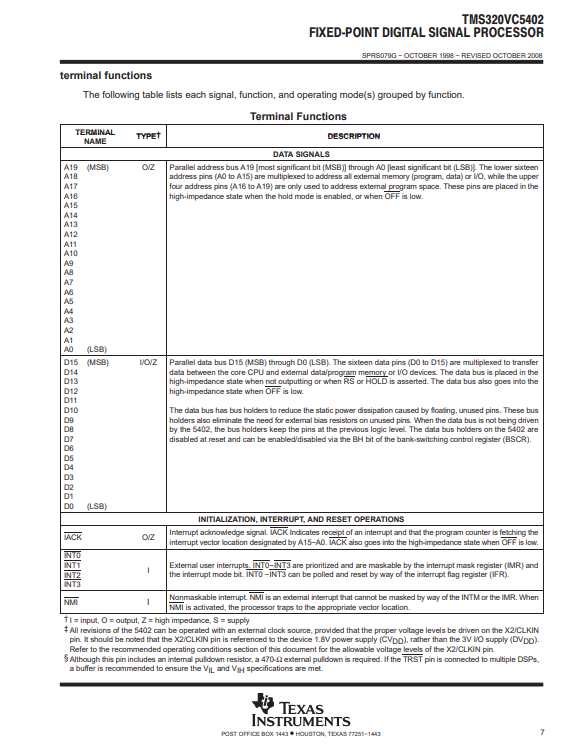

Il processore di segnale digitale (DSP) a virgola fissa TMS320VC5402 (di seguito denominato 5402 se non diversamente specificato) si basa su un'architettura Harvard modificata avanzata che dispone di un bus di memoria di programma e tre bus di memoria dati.Questo processore fornisce un'unità logica aritmetica (ALU) con un elevato grado di parallelismo, logica hardware specifica dell'applicazione, memoria su chip e periferiche aggiuntive su chip.La base della flessibilità operativa e della velocità di questo DSP è un set di istruzioni altamente specializzato.Gli spazi di programma e dati separati consentono l'accesso simultaneo alle istruzioni e ai dati del programma, fornendo un elevato grado di parallelismo.Due operazioni di lettura e un'operazione di scrittura possono essere eseguite in un singolo ciclo.Le istruzioni con archivio parallelo e le istruzioni specifiche dell'applicazione possono utilizzare completamente questa architettura.Inoltre, i dati possono essere trasferiti tra i dati e gli spazi del programma.Tale parallelismo supporta un potente insieme di operazioni aritmetiche, logiche e di manipolazione dei bit che possono essere eseguite in un singolo ciclo macchina.Inoltre, il 5402 include i meccanismi di controllo per gestire gli interrupt, le operazioni ripetute e le chiamate di funzione.

| Specifiche: | |

| Attributo | Valore |

| Categoria | Circuiti integrati (CI) |

| Incorporato - DSP (processori di segnali digitali) | |

| Mfr | Strumenti texani |

| Serie | TMS320C54x |

| Pacchetto | Vassoio |

| Stato della parte | Attivo |

| Tipo | Punto fisso |

| Interfaccia | Interfaccia host, McBSP |

| Frequenza di clock | 100MHz |

| Memoria non volatile | ROM (8kB) |

| RAM su chip | 32KB |

| Tensione - I/O | 3,30 V |

| Tensione - Nucleo | 1,80 V |

| temperatura di esercizio | -40°C ~ 100°C (TC) |

| Tipo di montaggio | Montaggio superficiale |

| Confezione/caso | 144-LQFP |

| Pacchetto dispositivo fornitore | 144-LQFP (20x20) |

| Numero del prodotto di base | TMS320 |

ImparentatoPRODOTTI

-

tel

-

E-mail

-

Skype

-

WhatsApp

WhatsApp