TMS320C6657CZHA IC DSP PUNTO FISSO/FLOAT 625FCBGA

Parametro del prodotto

Descrizione

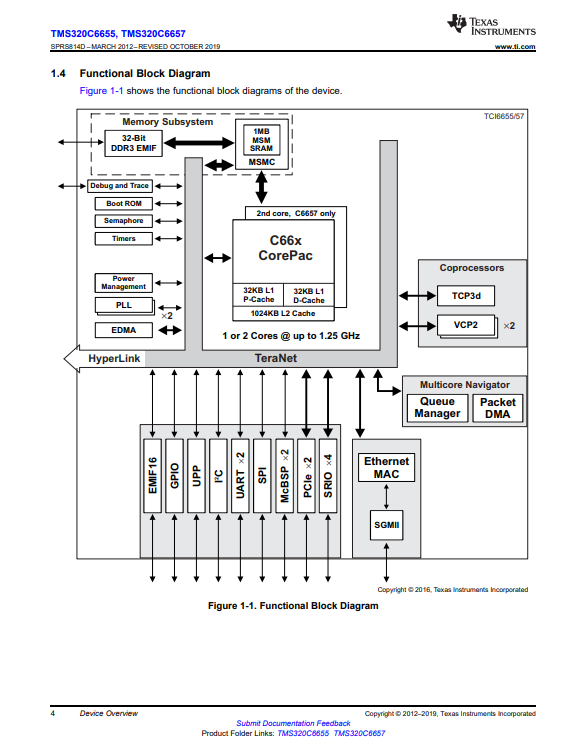

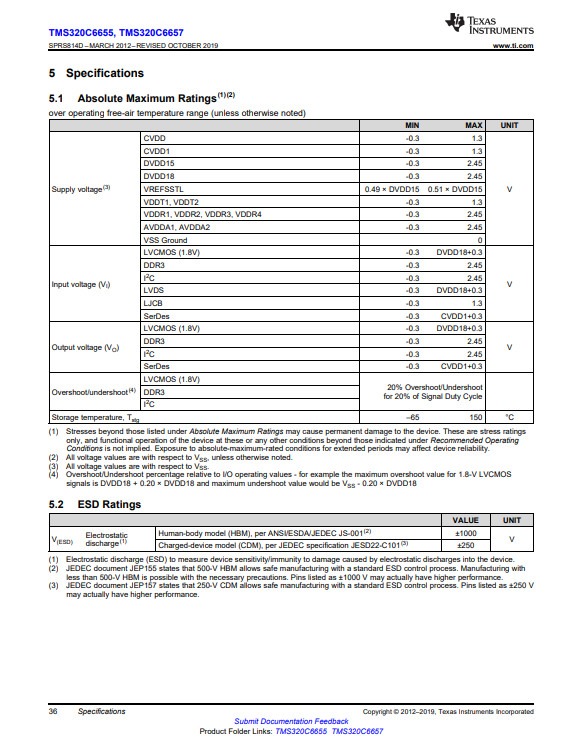

L'architettura KeyStone di TI fornisce una piattaforma programmabile che integra vari sottosistemi (core C66x, sottosistema di memoria, periferiche e acceleratori) e utilizza numerosi componenti e tecniche innovativi per massimizzare la comunicazione intradispositivo e interdispositivo che consente alle varie risorse DSP di operare in modo efficiente e senza interruzioni.Al centro di questa architettura ci sono componenti chiave come Multicore Navigator che consente una gestione efficiente dei dati tra i vari componenti del dispositivo.TeraNet è una struttura di switch non bloccante che consente un trasferimento dei dati interno rapido e senza contese.Il controller di memoria condivisa multicore consente l'accesso diretto alla memoria condivisa ed esterna senza attingere dalla capacità dello switch fabric.Per l'utilizzo a virgola fissa, il core C66x ha 4 volte la capacità di accumulo multiplo (MAC) dei core C64x+.Inoltre, il core C66x integra la capacità in virgola mobile e le prestazioni computazionali grezze per core sono 40 GMACS per core e 20 GFLOPS per core leader del settore (frequenza operativa di 1,25 GHz).Il core C66x può eseguire 8 operazioni MAC a virgola mobile a precisione singola per ciclo e può eseguire operazioni a precisione doppia e mista ed è conforme a IEEE 754.Il core C66x incorpora 90 nuove istruzioni (rispetto al core C64x+) destinate all'elaborazione in virgola mobile e orientata alla matematica vettoriale.Questi miglioramenti producono notevoli miglioramenti delle prestazioni nei popolari kernel DSP utilizzati nell'elaborazione del segnale, nelle funzioni matematiche e di acquisizione delle immagini.Il core C66x è compatibile con il codice precedente con i core DSP a virgola fissa e mobile C6000 della generazione precedente di TI, garantendo la portabilità del software e cicli di sviluppo del software ridotti per le applicazioni che migrano verso hardware più veloce.Il DSP C665x integra una grande quantità di memoria su chip.Oltre a 32 KB di programma L1 e cache dati, 1024 KB di memoria dedicata possono essere configurati come RAM mappata o cache.Il dispositivo integra inoltre 1024 KB di memoria condivisa multicore che può essere utilizzata come SRAM L2 condivisa e/o SRAM L3 condivisa.Tutte le memorie L2 incorporano il rilevamento e la correzione degli errori.Per un rapido accesso alla memoria esterna, questo dispositivo include un'interfaccia di memoria esterna (EMIF) DDR-3 a 32 bit che funziona a una velocità di 1333 MHz e dispone del supporto ECC DRAM.

| Specifiche: | |

| Attributo | Valore |

| Categoria | Circuiti integrati (CI) |

| Incorporato - DSP (processori di segnali digitali) | |

| Mfr | Strumenti texani |

| Serie | TMS320C66x |

| Pacchetto | Vassoio |

| Stato della parte | Attivo |

| Tipo | Fisso/virgola mobile |

| Interfaccia | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Frequenza di clock | 1 GHz |

| Memoria non volatile | ROM (128kB) |

| RAM su chip | 2,06MB |

| Tensione - I/O | 1,0 V, 1,5 V, 1,8 V |

| Tensione - Nucleo | 1,00 V |

| temperatura di esercizio | -40°C ~ 100°C (TC) |

| Tipo di montaggio | Montaggio superficiale |

| Confezione/caso | 625-BFBGA, FCBGA |

| Pacchetto dispositivo fornitore | 625-FCBGA (21x21) |

| Numero del prodotto di base | TMS320 |

ImparentatoPRODOTTI

-

tel

-

E-mail

-

Skype

-

WhatsApp

WhatsApp