OMAPL138EZWTD4 CI MPU OMAP-L1X 456MHZ 361NFBGA

Parametro del prodotto

Descrizione

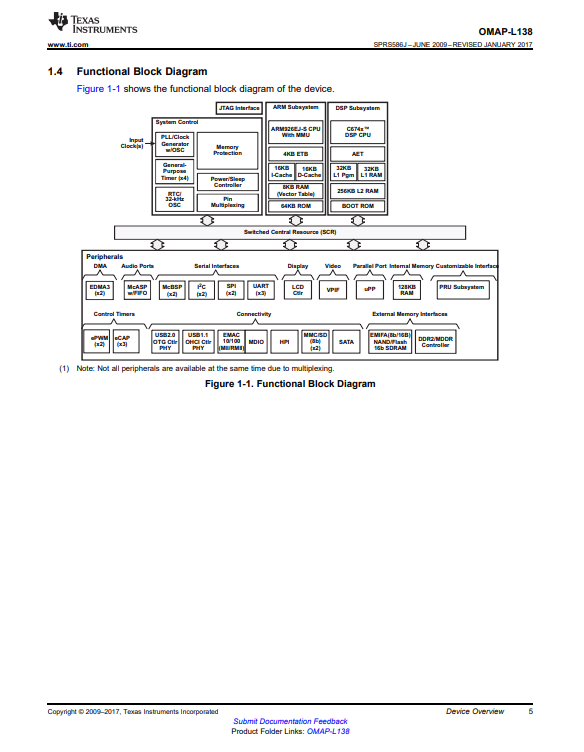

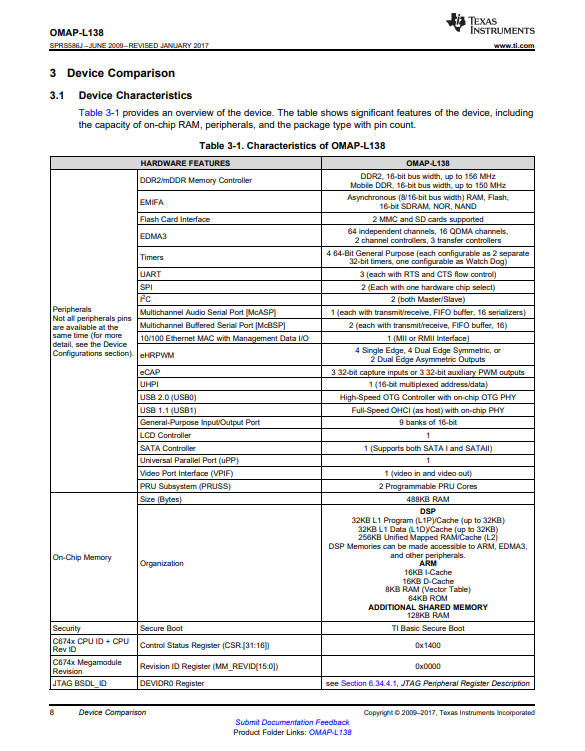

Il processore OMAP-L138 C6000 DSP+ARM è un processore per applicazioni a basso consumo basato su un ARM926EJ-S e un core DSP C674x.Questo processore fornisce una potenza significativamente inferiore rispetto ad altri membri della piattaforma TMS320C6000™ di DSP.Il dispositivo consente ai produttori di apparecchiature originali (OEM) e ai produttori di design originale (ODM) di portare rapidamente sul mercato dispositivi con sistemi operativi robusti, interfacce utente avanzate e prestazioni del processore elevate grazie alla massima flessibilità di una soluzione di processori misti completamente integrata.L'architettura dual-core del dispositivo offre i vantaggi delle tecnologie DSP e RISC (Reduced Instruction Set Computer), incorporando un core DSP TMS320C674x ad alte prestazioni e un core ARM926EJ-S.ARM926EJ-S è un core del processore RISC a 32 bit che esegue istruzioni a 32 bit o 16 bit ed elabora dati a 32, 16 o 8 bit.Il core utilizza il pipelining in modo che tutte le parti del processore e del sistema di memoria possano funzionare continuamente.Il core ARM9 ha un coprocessore 15 (CP15), un modulo di protezione e unità di gestione della memoria di dati e programmi (MMU) con buffer di tabella look-aside.Il core ARM9 ha istruzioni separate da 16 KB e cache di dati da 16 KB.Entrambe le cache sono associative a 4 vie con virtual index virtual tag (VIVT).Il core ARM9 ha anche 8KB di RAM (Vector Table) e 64KB di ROM.Il core DSP del dispositivo utilizza un'architettura basata su cache a 2 livelli.La cache del programma di livello 1 (L1P) è una cache a mappatura diretta da 32 KB e la cache dei dati di livello 1 (L1D) è una cache a 2 vie con associazione di insiemi da 32 KB.La cache del programma di livello 2 (L2P) consiste in uno spazio di memoria di 256 KB condiviso tra il programma e lo spazio dati.La memoria L2 può essere configurata come memoria mappata, cache o una combinazione delle due.Sebbene il DSP L2 sia accessibile dall'ARM9 e da altri host nel sistema, sono disponibili ulteriori 128 KB di memoria RAM condivisa per l'utilizzo da parte di altri host senza influire sulle prestazioni del DSP.

| Specifiche: | |

| Attributo | Valore |

| Categoria | Circuiti integrati (CI) |

| Incorporato - Microprocessori | |

| Mfr | Strumenti texani |

| Serie | OMAP-L1x |

| Pacchetto | Vassoio |

| Stato della parte | Attivo |

| Processore principale | ARM926EJ-S |

| Numero di core/larghezza del bus | 1 nucleo, 32 bit |

| Velocità | 456 Mhz |

| Co-processori/DSP | Elaborazione del segnale;C674x, controllo del sistema;CP15 |

| Controller RAM | SDRAM |

| Accelerazione grafica | No |

| Display e controller di interfaccia | LCD |

| Ethernet | 10/100Mbps (1) |

| SATA | SATA 3Gbps (1) |

| USB | USB 1.1 + PHY (1), USB 2.0 + PHY (1) |

| Tensione - I/O | 1,8 V, 3,3 V |

| temperatura di esercizio | -40°C ~ 90°C (TJ) |

| Caratteristiche di sicurezza | Sicurezza di avvio, crittografia |

| Confezione/caso | 361-LFGBA |

| Pacchetto dispositivo fornitore | 361-NFGA (16x16) |

| Interfacce aggiuntive | HPI, I²C, McASP, McBSP, MMC/SD, SPI, UART |

| Numero del prodotto di base | OMAPL138 |

ImparentatoPRODOTTI

-

tel

-

E-mail

-

Skype

-

WhatsApp

WhatsApp