EP1C6Q240C8N CI FPGA 185 I/O 240QFP

Parametro del prodotto

Descrizione

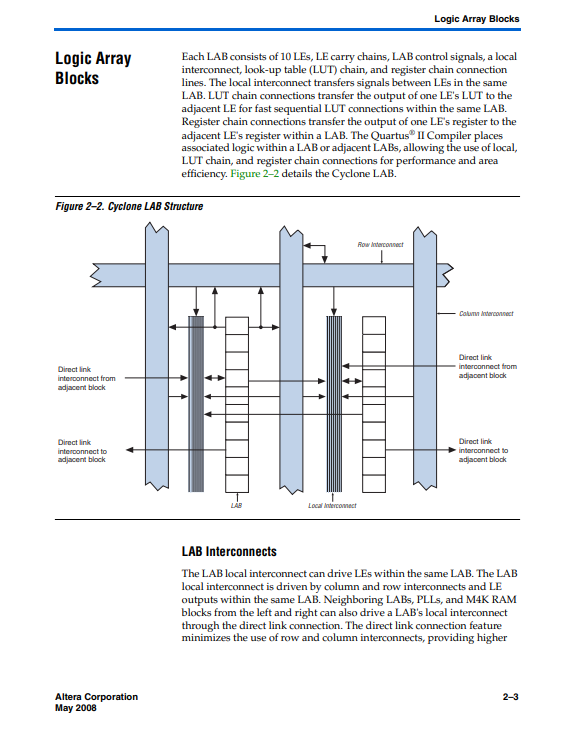

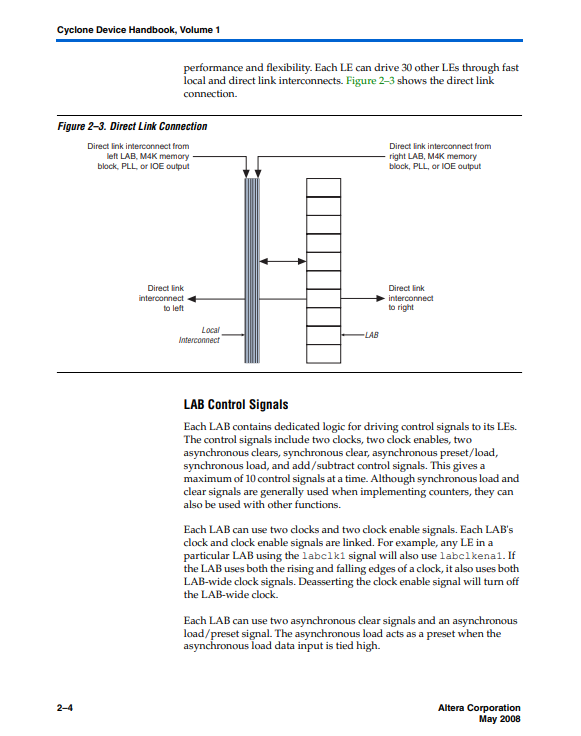

I dispositivi Cyclone® contengono un'architettura bidimensionale basata su righe e colonne per implementare la logica personalizzata.Le interconnessioni di colonne e righe a velocità variabili forniscono interconnessioni di segnali tra LAB e blocchi di memoria incorporati.L'array logico è costituito da LAB, con 10 LE in ciascun LAB.Un LE è una piccola unità logica che fornisce un'implementazione efficiente delle funzioni logiche utente.I LAB sono raggruppati in righe e colonne in tutto il dispositivo.I dispositivi Cyclone vanno da 2.910 a 20.060 LE.I blocchi RAM M4K sono veri e propri blocchi di memoria dual-port con 4K bit di memoria più parità (4.608 bit).Questi blocchi forniscono memoria dedicata a doppia porta reale, doppia porta semplice o porta singola fino a 36 bit di larghezza fino a 250 MHz.Questi blocchi sono raggruppati in colonne nel dispositivo tra determinati LAB.I dispositivi Cyclone offrono tra 60 e 288 Kbit di RAM incorporata.Ogni pin I/O del dispositivo Cyclone è alimentato da un elemento I/O (IOE) situato alle estremità delle righe e delle colonne LAB attorno alla periferia del dispositivo.I pin I/O supportano vari standard I/O single-ended e differenziali, come lo standard PCI a 66 e 33 MHz, 64 e 32 bit e lo standard I/O LVDS fino a 640 Mbps.Ogni IOE contiene un buffer I/O bidirezionale e tre registri per la registrazione dei segnali di input, output e output-enable.I pin DQS, DQ e DM a doppio scopo insieme alle catene di ritardo (utilizzate per allineare in fase i segnali DDR) forniscono il supporto dell'interfaccia con dispositivi di memoria esterni come DDR SDRAM e dispositivi FCRAM fino a 133 MHz (266 Mbps).I dispositivi Cyclone forniscono una rete di clock globale e fino a due PLL.La rete di clock globale è composta da otto linee di clock globali che attraversano l'intero dispositivo.La rete di clock globale può fornire clock per tutte le risorse all'interno del dispositivo, come IOE, LE e blocchi di memoria.Le linee di clock globali possono essere utilizzate anche per i segnali di controllo.I Cyclone PLL forniscono un clock generico con moltiplicazione del clock e sfasamento, nonché uscite esterne per il supporto di I/O differenziali ad alta velocità.

| Specifiche: | |

| Attributo | Valore |

| Categoria | Circuiti integrati (CI) |

| Incorporato - FPGA (Field Programmable Gate Array) | |

| Mfr | Intel |

| Serie | Ciclone® |

| Pacchetto | Vassoio |

| Stato della parte | Obsoleto |

| Numero di LAB/CLB | 598 |

| Numero di elementi logici/celle | 5980 |

| Totale bit RAM | 92160 |

| Numero di I/O | 185 |

| Tensione - Alimentazione | 1,425 V ~ 1,575 V |

| Tipo di montaggio | Montaggio superficiale |

| temperatura di esercizio | 0°C ~ 85°C (TJ) |

| Confezione/caso | 240-BFQFP |

| Pacchetto dispositivo fornitore | 240-PQFP (32x32) |

| Numero del prodotto di base | EP1C6 |

ImparentatoPRODOTTI

-

tel

-

E-mail

-

Skype

-

WhatsApp

WhatsApp