AD9516-3BCPZ IC OROLOGIO PLL/VCO 2GHZ 64LFCSP

Parametro del prodotto

Descrizione

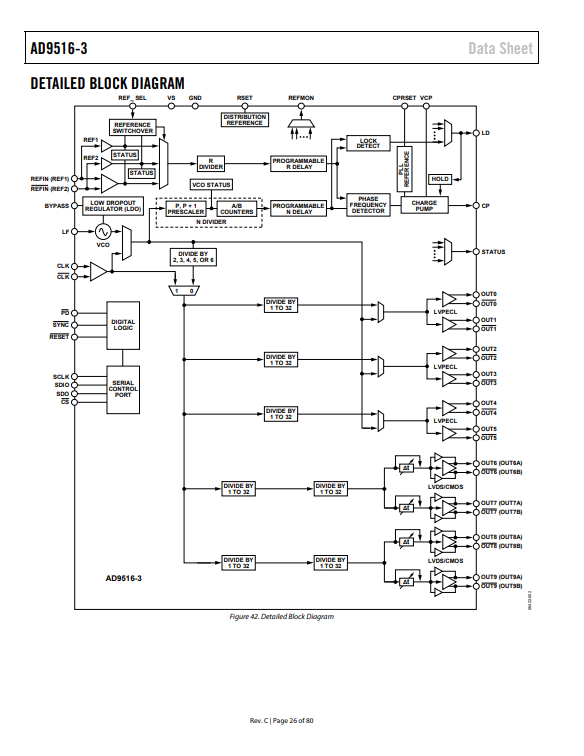

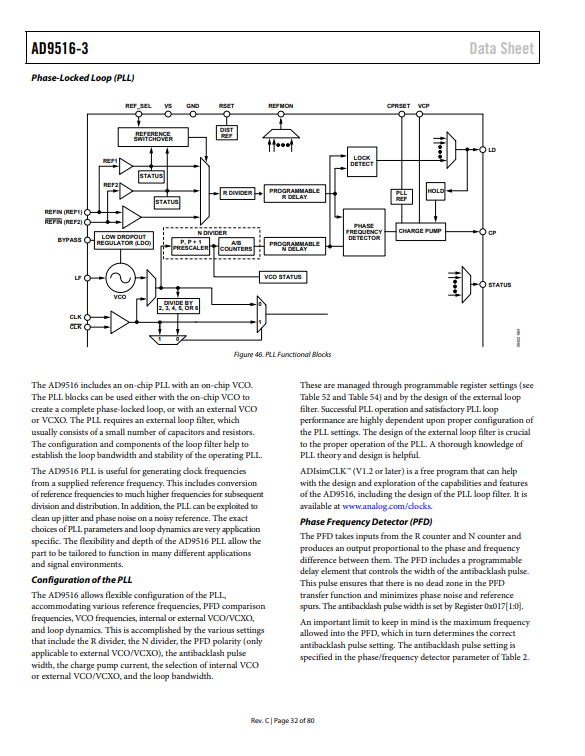

AD9516-31 fornisce una funzione di distribuzione del clock multi-uscita con prestazioni di jitter subpicosecondo, insieme a PLL e VCO su chip.Il VCO on-chip si sintonizza da 1,75 GHz a 2,25 GHz.Facoltativamente, è possibile utilizzare un VCO/VCXO esterno fino a 2,4 GHz.AD9516-3 enfatizza il basso jitter e il rumore di fase per massimizzare le prestazioni del convertitore di dati e può beneficiare di altre applicazioni con requisiti di rumore di fase e jitter impegnativi.SCHEMA A BLOCCHI FUNZIONALI REFIN REF1 REF2 CLK LF SWITCHOVER E MONITOR PLL DIVIDER E MUX CP VCO STATUS MONITOR LVPECL LVPECL LVPECL LVDS/CMOS LVDS/CMOS PORTA DI CONTROLLO SERIALE E LOGICA DIGITALE AD9516-3 OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 OUT9 DIV/Φ DIV/Φ DIV/Φ DIV/Φ DIV/Φ DIV/Φ DIV/Φ Δt Δt Δt Δt 06422-001 Figura 1. AD9516-3 presenta sei uscite LVPECL (in tre coppie) e quattro uscite LVDS (in due coppie) .Ogni uscita LVDS può essere riconfigurata come due uscite CMOS.Le uscite LVPECL operano a 1,6 GHz, le uscite LVDS operano a 800 MHz e le uscite CMOS operano a 250 MHz.Ciascuna coppia di uscite dispone di divisori che consentono di impostare sia il rapporto di divisione che il ritardo grossolano (o fase).L'intervallo di divisione per le uscite LVPECL è compreso tra 1 e 32. Le uscite LVDS/CMOS consentono un intervallo di divisioni fino a un massimo di 1024. AD9516-3 è disponibile in un LFCSP a 64 conduttori e può essere azionato da un singolo 3.3 Alimentazione V.Un VCO esterno, che richiede un intervallo di tensione esteso, può essere adattato collegando l'alimentazione della pompa di carica (VCP) a 5 V. Un alimentatore LVPECL separato può essere compreso tra 2,5 V e 3,3 V (nominale).AD9516-3 è specificato per il funzionamento nell'intervallo industriale standard da -40°C a +85°C.

| Specifiche: | |

| Attributo | Valore |

| Categoria | Circuiti integrati (CI) |

| Clock/Timing - Generatori di clock, PLL, sintetizzatori di frequenza | |

| Mfr | Analog Devices Inc. |

| Serie | - |

| Pacchetto | Vassoio |

| Stato della parte | Attivo |

| Tipo | Generatore di clock, distribuzione fanout |

| PL | SÌ |

| Ingresso | Orologio |

| Produzione | CMOS, LVDS, LVPECL |

| Numero di circuiti | 1 |

| Rapporto - Ingresso:Uscita | 1:14 |

| Differenziale - Ingresso:Uscita | Si si |

| Frequenza - max | 2,95 GHz |

| Divisore/Moltiplicatore | Si No |

| Tensione - Alimentazione | 3,135 V ~ 3,465 V |

| temperatura di esercizio | -40°C ~ 85°C |

| Tipo di montaggio | Montaggio superficiale |

| Confezione/caso | 64-VFQFN Piazzola esposta, CSP |

| Pacchetto dispositivo fornitore | 64-LFCSP-VQ (9x9) |

| Pacchetto dispositivo fornitore | 64-LFCSP-VQ (9x9) |

| Numero del prodotto di base | AD9516 |

ImparentatoPRODOTTI

-

tel

-

E-mail

-

Skype

-

WhatsApp

WhatsApp